PLL frequency acquisition - Smart circuit with no phase frequency detector or lock detector

Ref.-No. 6339

Keywords: Bang-bang phase detector, Hogge phase detector,clock and data recovery. frequency acquisition, optical transceiversoptical transceivers, PLL

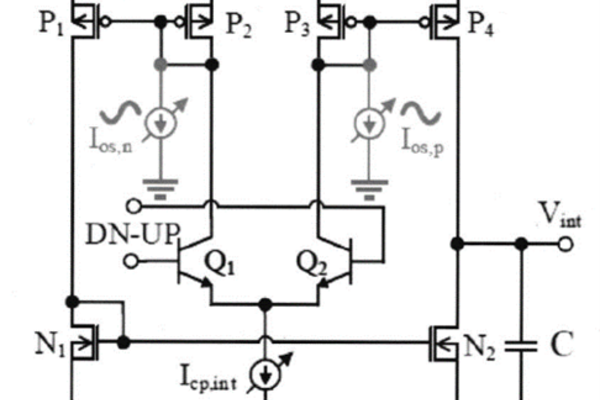

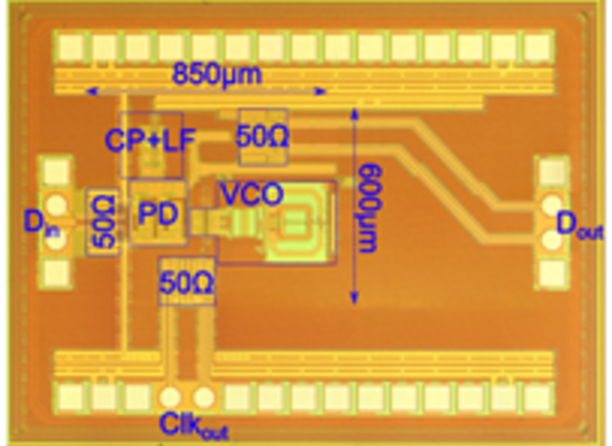

A phase-locked loop, or PLL, is a control system that is widely employed in telecommunications technology as well as measurement and control systems as frequency sources, to demodulate frequency- or phase-modulated signals, and for clock synchronization and recovery. This novel PLL circuit from Paderborn University is vastly less complex than conventional PLLs with a separate “loss of lock” circuit, meaning it also consumes less power. The best part about the circuit is that it continuously uses a slow sine wave. This type of sine wave is usually only used when a loss of lock has occurred, where a separate circuit is then required. Although the use of a sine wave produces a minor phase difference, it is inconsequential compared to other noise sources. This invention adjusts the continuous sine wave via the phase detector's output signals. Specifically, the electronic circuit consists of a charge pump and a low-pass filter as shown in the figure below. It also contains three current mirrors, charging the capacity based on the DN/UP C inputs in order to compensate for phase differences in a PLL while also applying a continuous sine wave to the upper current mirrors (los,n and los,p) that is slower compared to the oscillator frequency and with which the PLL can be recaptured in case of a loss of lock.

Competitive Advantages

- ASIC available

- Simple circuit design

- Low power consumption

- Low phase difference

- Good jitter response

Commercial Opportunities

This new circuit from Paderborn University can be used in telecommunications technology or measurement and control systems, particularly where continuous, slow sine waves are employed, such as bang-bang PLLs, Hogge PLLs, Baud-rate CDRs, and optical transceiver circuits.

Current Status

A patent has been filed with the EPO in Luxembourg and published under EP3168949A1. We are offering interested companies the opportunity to license and continue to develop this technology with the inventors at the university.

Relevant Puclications

2021 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS) - Reference-less Bang-bang CDR with Enhanced Frequency Acquisition Range Using Static and Modulated Integral Branch Offset Currents

—

An invention of Paderborn University.