Optimierte Chiptests - Rekonfigurierbare Teststrukturen für schnelle IC-Tests

Ref.-Nr. 4991

Keywords: JTAG, ISO26262, gleichzeitiger IC-Test, Mikrochips mit rekonfigurierbaren Teststrukturen, Concurrent IJTAG

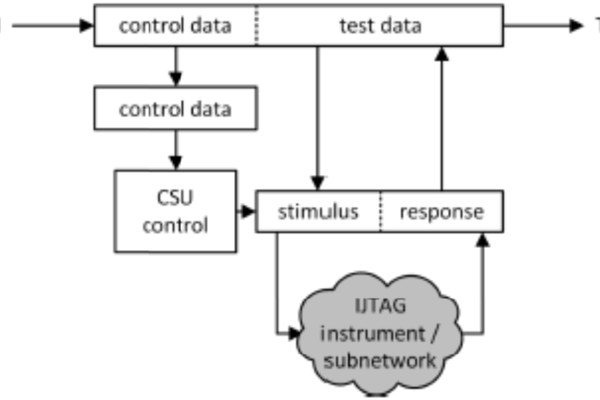

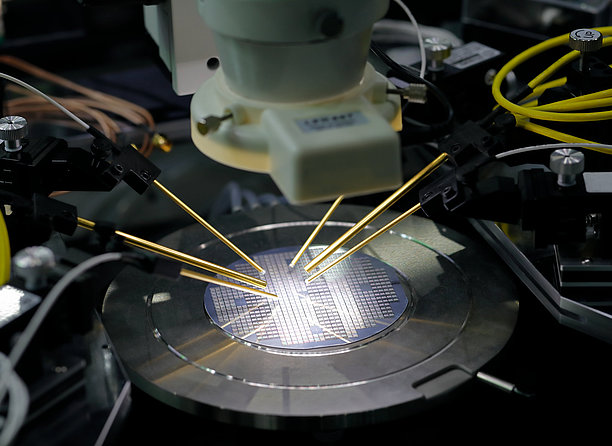

Intergrierte Schaltungen, auch ICs genannt, müssen getestet werden – nur so lässt sich die gefordertete Funktionanlität gewährleisten. Dazu werden die Schaltkreise mit zusätzlichen Teststrukuren versehen, genauer gesagt mit einem Testeingang (TDI) und einen Testausgang (TDO). Bei den bisher bekannten Teststrukturen legt man über den Testeingang Testsignale an und leitet diese durch alle Strukturen hindurch. Üblicherweise steht dazu nur ein Testzugang zur Verfügung, denn die Fläche, die für Zugänge zur Verfügung steht, ist limitiert. Die Folge: Lange Testdauern und somit kostenintensive Tests. In vielen Anwendungen sind Selbsttests des ICs, die während des Betriebs durchgeführt werden, aus Sicherheitsgründen notwendig. Beschrieben werden solche schnellen Selbsttests im Betrieb (In-Field-Test) von der IEEE1687.

Das neue Verfahren aus der Hochschule Hamm-Lippstadt bietet für diese Problematik eine effiziente Lösung: Es nutzt zum Test eine Vielzahl von rekonfigurierbaren Teststrukturen, die mit einem Zwischenspeicher verbunden sind. Auf diese Weise kann in den Teststrukturen nebenläufig getestet werden – die Tests gehen deutlich schneller vonstatten. Dabei hilft ein Zwischenspeicher sowie eine entsprechende individuelle Steuerung. Eine weitere Effizienzsteigerung wird durch die Verwendung von komprimierten Testdaten erreicht.

Vorteile

- Zeitersparnis

- Kostenreduktion beim IC-Test

- Gute Integrationsfähigkeit in Testprozesse

Kommerzielle Anwendung

Obwohl Chipproduzenten bereits einen erheblichen Zeit- und Kostenaufwand in die Tests von ICs investieren, bleiben Fehler durch eine mangelnde Testabdeckung oft unentdeckt. Dazu kommt: Es werden große Mengen an Testdaten generiert, deren Analyse aufwendig ist. Beides geht mit hohen Kosten für die Hersteller von Mikrochips einher. Das neue Verfahren reduziert die benötigte Chipfläche und Testzeit erheblich.

Aktueller Stand

Eine Hardware-Realisierung der Erfindung liegt bisher nicht vor, jedoch konnte die prinzipielle technische Realisierbarkeit im Rahmen eines NRW-Patentvalidierungsprojekts nachgewiesen werden. Das deutsche Patent wurde unter dem Aktenzeichen DE 10 2017 216 444.1 beim Deutschen Marken- und Patentamt erteilt. Eine EP-Anmeldung unter dem Aktenzeichen EP 18 769 698.4 und eine US-Anmeldung unter dem Aktenzeichnen US 16/616,161 sind offengelegt. Wir bieten interessierten Unternehmen die Möglichkeit der Lizenzierung sowie die Weiterentwicklung der Technologie in Zusammenarbeit mit den Erfindern an der Hochschule Hamm-Lippstadt an.

Technologie-Reifegrad

1

2

3

4

5

6

7

8

9

Versuchsaufbau im Labor

Relevante Veröffentlichungen

Concurrent IJTAG. Rene Krenz-Baath; Hochschule Hamm-Lippstadt, Workshop Test und Zuverlässigkeit (TuZ‘18), 2018

—

Eine Erfindung der Hochschule Hamm-Lippstadt.