PICOihc - High Bandwidth Integrate-and-Hold Circuit

Ref.-Nr. 5197

Keywords: High Bandwidth integrate-and-hold circuit (IHC)

The invention pertains to an integrate-and-hold circuit which is used as a sampler. The typical structure of an integrate-and-hold circuit (IHC) is a multiplier serving as a switch followed by a resettable integrator with a hold capacitor. For a desired signal-to-noise ratio and signal swing the value of the hold capacitor has a minimum acceptable value which always limits the bandwidth.

Many advanced IHC circuit topologies utilize a delayed version of the integrate command signal to derive a track command fed to the switch control. The delay avoids switching noise at the beginning of the tracking. Moreover a tunable delay time facilitates bandwidth adjustment and, hence, SNR adjustment. However, the tunable delay line has a minimum delay, which – again – limits the achievable bandwidth.

It was the aim of scientists of Paderborn University to decouple the sampler bandwidth from the choice of hold capacitance value and to allow for very high bandwidth which in addition should be tunable.

Vorteile

- Very high bandwidth

- Tunable bandwidth

- Extremely short delay times possible

- Simple layout

- Prototype available

Kommerzielle Anwendung

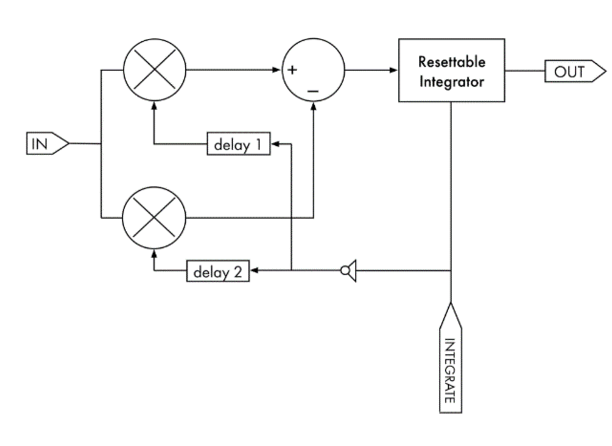

The figure above depicts one layout of the novel circuit. Two shunted switches (herein multipliers) both receive the input signal. A differential amplifier subtracts the outputs of both switches and delivers the difference to the input of the resettable integrator. Two tunable delay elements feed track command inputs of both switches, wherein both delay element inputs receive the inverted integrate command.

The integration time is the difference between the delay times delay1 and delay2. The unique characteristic of the novel circuit is, that the delay difference can be adjusted to much shorter delays and with a considerably higher resolution than a single delay.

This novel IHC topology enables extremely short delays independent from the minimum delay times of the utilized delay elements.

Aktueller Stand

The invention is patent pending. Do not hesitate to asking us for grant procedure details. A prototype exists which demonstrates the benefit of the invention. On behalf of Paderborn University, PROvendis offers licenses to interested companies for the invention and the patent application.

—

Eine Erfindung der Uni Paderborn.